DDR2 SDRAM

概述

像所有的SDRAM实现方法一样,DDR2 SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。像之前的DDR,DDR2 I/O 缓冲器在时钟信号的上升沿和下降沿都传输数据(一种叫做"double pumping"的技术)。DDR和DDR2的关键区别是:DDR2内存单元的核心频率是等效频率的1/4(而不是1/2)。这需要一个4-bit-deep的预取队列,在并不用改变内存单元本身的情况下,DDR2能有效地达到DDR数据传输速度的两倍。

DDR2的等效频率由于电气接口的改进(包括on-die termination, prefetch buffers 和 off-chip drivers)而大增。然而,CAS等待时间却增长了。DDR2预读取是4位,而DDR预读取是2位,DDR3预读取是8位。DDR SDRAM一般是2到3个总线周期的读取等待时间,而DDR2一般是4到6个总线周期的读取等待时间。

另外增加的带宽导致的成本是芯片封装更昂贵且更困难,因为BGA封装相比于先前采用TSSOP封装技术生产的DDR SDRAM和SDR SDRAM更昂贵且更困难。这种封装的改变需要更高的总线速度以维持信号的完整。

节能得以实现主要是由于生产过程中的模具收缩导致工作电压的下降(从DDR的2.5V到DDR2的1.8V)。更低的内存时钟频率也能使应用程序不需要最高的可用数据传输率而得以降低功耗。

根据JEDEC 建议的最高电压是1.9V,并且建议对于要求内存稳定使用的环境绝不能超过此值(例如服务器或其他任务关键设备)。此外,JEDEC规定内存模块必须在受到永久损害前承受2.3V的电压(虽然它们可能正常工作时并不在此电压水平)。

规范标准

芯片和模块

现时有售的DDR2-SDRAM已能达到DDR2-1200,但必须在高电压下运作,以维持其稳定性。

历史

2003年第二季度,DDR2推出了两种频率的内存:其内部时钟频率分别为200MHz(对应PC2-3200)和266MHZ(PC2-4200)。它们在延迟方面的表现不如原来的DDR内存,使得总访问时间更长。然而,原来的DDR技术时钟频率可超出200MHz(400MT/s)。更高性能的DDR芯片虽存在,但是JEDEC已表示他们不会将其标准化。

2004年底由于模块到达更低的延迟变成现实,DDR2相比更早的DDR标准变得具有竞争力。

向后兼容

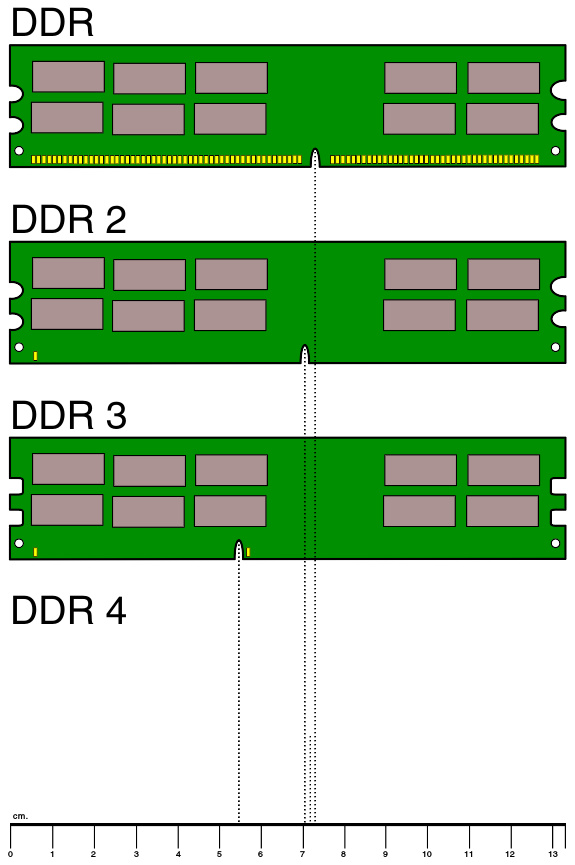

台式机所使用之DDR、DDR2 以及DDR3 存储器的差异

DDR2 DIMMs没有被设计成与DDR DIMMs向后兼容。DDR2 DIMMs的凹口位置与DDR DIMMs是不同的,并且用于台式机的内存针脚数DDR2高于DDR DIMMs。DDR2有240针,DDR有184针。用于笔记本电脑的有200针的DDR和DDR2,但是DDR凹口的位置与DDR2有微小的不同。

高性能的DDR2 DIMMs与低性能的DDR2 DIMMs是兼容的;但是,混用高性能的内存只能以低性能内存的频率工作。在系统中,更高性能的总线与低性能的DDR2内存结合,则最终性能由低性能的内存决定;然而在许多系统中这种性能损失可以通过设置内存计时以致更低的延时来减缓。

ddr2l

是指笔记本电脑上的暂存存储器,以acer,asus电脑为例,内均建南亚科技,少数高级机种采用威刚科技。

南亚科ddr2l

延伸阅读

JEDEC standard: DDR2 SDRAM Specification(JESD79-2F, November 2009)

JEDEC standard: DDR2-1066

JEDEC Standard No. 21C: 4.20.13 240-Pin PC2-5300/PC2-6400 DDR2 SDRAM Unbuffered DIMM Design Specification (PDF) .JEDECSolid State Technology Association. 2008-10 [ 2008-12-26 ] .

Razak Mohammed Ali.DDR2 SDRAM interfaces for next-gen systems (PDF) . Electronic Engineering Times.

参见

SDR SDRAM

DDR SDRAM

DDR3 SDRAM

RDRAM

双通道

FB-DIMM

免责声明:以上内容版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。感谢每一位辛勤著写的作者,感谢每一位的分享。

- 有价值

- 一般般

- 没价值

推荐阅读

关于我们

APP下载