MIPS架构

发展历史在1981年,史丹佛大学教授约翰·轩尼诗领导他的团队,实现出第一个MIPS架构的处理器。他们原始的概令是通过指令管线化来增加CPU运算的速度。1984年,约翰·轩尼诗教授离开斯坦福大学,创立MIPS科技公司。于1985年,设计出R2000芯片,1988年,将其改进为R3000芯片。MIPS指令格式在MIPS架构中,指令被分为三种类型:R型、I型和J型。三种类型的指令的最高6位均为6位的opcode码。从25位往下,R型指令用连续三个5位二进制码来表示三个寄存器的地址,然后用一个5位二进制码来表示移位的位数(如果未使用移位操作,则全为0),最后为6位的function码(它与opcode码共同决定R型指令的具体操作方式);I型指令则用连续两个5位二进制码来表示两个寄存器的地址,然后是一个16位二进制码来表示的一个立即数二进制码;J型指令用26位二进制码来表示跳转目标的指令地址(实际的...

发展历史

在1981年,史丹佛大学教授约翰·轩尼诗领导他的团队,实现出第一个MIPS架构的处理器。他们原始的概令是通过指令管线化来增加CPU运算的速度。

1984年,约翰·轩尼诗教授离开斯坦福大学,创立MIPS科技公司。于1985年,设计出R2000芯片,1988年,将其改进为R3000芯片。

MIPS指令格式

在MIPS架构中,指令被分为三种类型:R型、I型和J型。三种类型的指令的最高6位均为6位的opcode码。从25位往下,

R型指令用连续三个5位二进制码来表示三个寄存器的地址,然后用一个5位二进制码来表示移位的位数(如果未使用移位操作,则全为0),最后为6位的function码(它与opcode码共同决定R型指令的具体操作方式);

I型指令则用连续两个5位二进制码来表示两个寄存器的地址,然后是一个16位二进制码来表示的一个立即数二进制码;

J型指令用26位二进制码来表示跳转目标的指令地址(实际的指令地址应为32位,其中最低两位为00,高四位由PC当前地址决定)。

三种类型的指令图示如下:

相关条目

龙芯

免责声明:以上内容版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。感谢每一位辛勤著写的作者,感谢每一位的分享。

——— 没有了 ———

编辑:阿族小谱

文章价值打分

- 有价值

- 一般般

- 没价值

当前文章打 0 分,共有 0 人打分

文章观点支持

0

0

文章很值,打赏犒劳一下作者~

发表评论

写好了,提交

{{item.label}}

{{commentTotal}}条评论

{{item.userName}}

发布时间:{{item.time}}

{{item.content}}

回复

举报

打赏作者

“感谢您的打赏,我会更努力的创作”

— 请选择您要打赏的金额 —

{{item.label}}

{{item.label}}

打赏成功!

“感谢您的打赏,我会更努力的创作”

返回

打赏

私信

推荐阅读

· ARM架构

特色和应用自2005年,每年超过一亿的手机销售约98%至少使用了一个ARM处理器。截至2009年,占大约90%的所有嵌入式32位RISC处理器和ARM处理器被广泛使用在消费性电子产品,包括个人数字助理(PDA)、平板电脑、移动电话、数字媒体和音乐播放器、手持式游戏游戏机、计算器和计算机外围设备(如硬盘驱动器和路由器)。历史一颗主要用于路由器的科胜讯公司ARM处理器用于松下多媒体播放机的芯片ARM的设计是艾康电脑公司于1983年开始的开发项目。这个团队由RogerWilson和SteveFurber带领,着手开发一种类似高级6502架构的处理器。Acorn电脑有一大堆建构在6502处理器上的电脑,因此能设计出一颗类似的芯片即意味着对公司有很大的优势。AcornRISCMachine:ARM2用在BBCMicro上的ARM1secondprocessor团队在1985年时开发出样本“ARM1”...

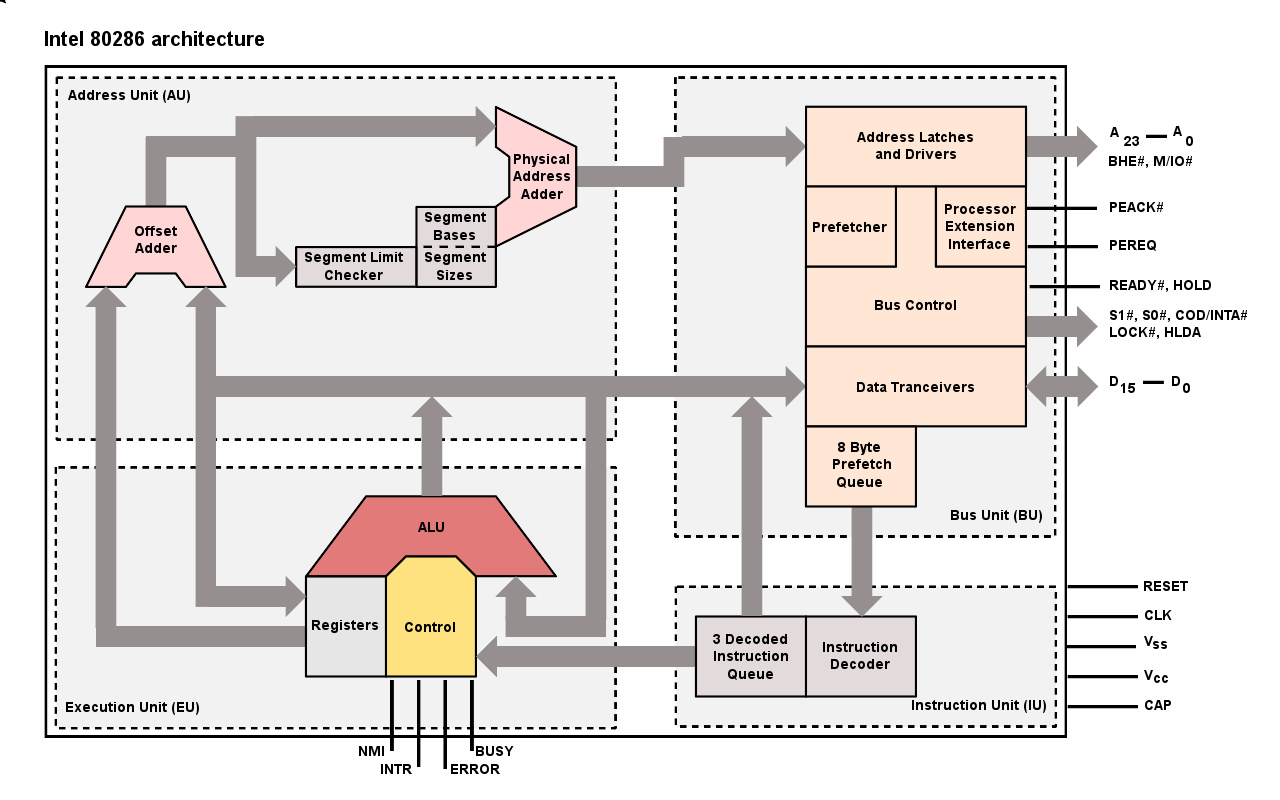

· 微架构

和指令集架构的关系指令集架构是指在处理器内被处理的程式,指令集架构为组合语言的设计师和编译器所见。指令集架构包含executionmodel,暂存器,地址以及资料格式。微架构包含处理器内部的构成以及这些构成起来的部分如何执行指令集架构。微架构通常被表示成流程图,以描述机器内部元件的连结状况,从一个闸或是暂存器,到算术逻辑单元(ALU)。图上分布着资料路径(可以显示资料在微架构的位置)以及控制路径(显示资料该被什么指令所处理)。每个微架构的的元件都被表示成藉数个逻辑门所建构而成的工具。每个逻辑门都被表示成藉晶体管建构成的零件。拥有不同微架构的机器可能拥有相同的指令集架构,因此可以执行相同的程式。由于半导体科技的进步,新型的处理器可以以较快的速度执行相同的指令集架构。微架构的概念Intel80286微架构在今日,管线资料路径是微架构中最常被使用的资料路径。这种作法也被普遍的用于微处理器,微控制...

· 软件架构

介绍软件体系结构是构建计算机软件实践的基础。与建筑师设定建筑项目的设计原则和目标,作为绘图员画图的基础一样,软件架构师(英语:Softwarearchitect)或者系统架构师陈述软件架构以作为满足不同客户需求的实际系统设计方案的基础。从和目的、主题、材料和结构的联系上来说,软件架构可以和建筑物的架构相比拟。一个软件架构师需要有广泛的软件理论知识和相应的经验来实施和管理软件产品的高级设计。软件架构师定义和设计软件的模块化,模块之间的交互,用户界面风格,对外接口方法,创新的设计特性,以及高层事物的对象操作、逻辑和流程。软件架构师与客户商谈概念上的事情,与经理商谈广泛的设计问题,与软件工程师商谈创新的结构特性,与程序员商谈实现技巧,外观和风格。软件架构是一个系统的草图。软件架构描述的对象是直接构成系统的抽象组件。各个组件之间的连接则明确和相对细致地描述组件之间的通讯。在实现阶段,这些抽象组件被...

· Haswell微架构

技术特性作为英特尔“Tick-Tock”策略下的产物,在“Tick-Tock”时间表上,Haswell架构属于“Tock”阶段,是为架构改进换代。根据Fudzilla的消息,“英特尔透露给合作伙伴的消息指同时钟频率下与IvyBridge架构的产品相比,Haswell架构的产品其性能至少有10%的提升”。而英特尔宣称Haswell整体性能将比IvyBridge快两倍。英特尔称在某些工作负荷上Haswell架构的效率比上代产品的提升了20%。一片基于Haswell架构的处理器芯片的晶圆,与一只铁钉的大小对比已确认的新特性制程更成熟的22奈米制程,大幅改善漏电率(这里的漏电指高制程芯片于运作时,部分电子因量子穿隧效应而由非电路或电路组件的硅中穿过);更成熟的3D-三栅极晶体管;处理器核心14级管线(从IntelCore微架构开始一直沿用至今);和以往一样,整数运算、浮点运算和SIMD运算作业同样...

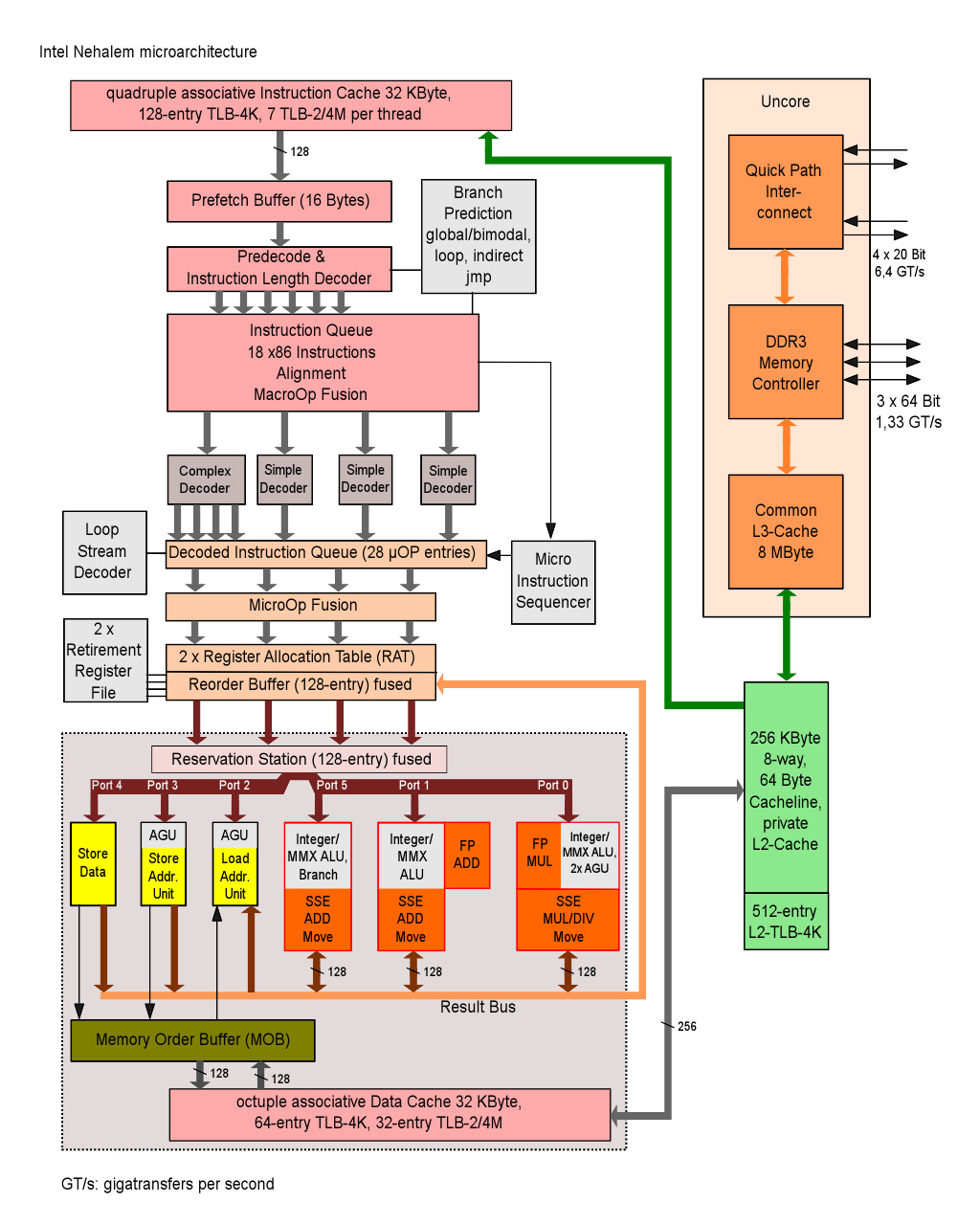

· Nehalem微架构

技术特点原生四核心的Nehalem微架构集成北桥全部型号的微处理器核心都集成了存储器控制器,一般支持双通道DDR3SDRAM,消费级产品最高支持三通道DDR3SDRAM,而服务器平台则可以支持四通道DDR3SDRAM;除此以外还处理器核心还集成了PCIExpress2.0控制器。直连式总线从Nehalem微架构开始,Intel改用QPI/DMI直连式总线,放弃了传统的FSB。首发的Corei7使用了新的“QuickPathInterconnect”直连式总线,与AMD的HyperTransport相似。相比FSB,每一个处理器都可以有独立的QPI通道与其他处理器连接,处理器之间不用再共享FSB带宽,并绕路到北桥才能通信。此外,QPI是双向传输。后来发布的Corei5、i3,处理器内部仍使用QPI,但与外部芯片组连接则使用与QPI类似但较QPI的带宽小的DMI(DirectMediaInte...

关于我们

关注族谱网 微信公众号,每日及时查看相关推荐,订阅互动等。

APP下载

下载族谱APP 微信公众号,每日及时查看

扫一扫添加客服微信