ARM架构

特色和应用

自2005年,每年超过一亿的手机销售约98%至少使用了一个ARM处理器。 截至2009年,占大约90%的所有嵌入式32位RISC处理器 和ARM处理器被广泛使用在消费性电子产品,包括个人数字助理(PDA)、平板电脑、移动电话、数字媒体和音乐播放器、手持式游戏游戏机、计算器和计算机外围设备(如硬盘驱动器和路由器)。

历史

一颗主要用于路由器的科胜讯公司ARM处理器

用于松下多媒体播放机的芯片

ARM的设计是艾康电脑公司于1983年开始的开发项目。

这个团队由Roger Wilson和Steve Furber带领,着手开发一种类似高级6502架构的处理器。Acorn电脑有一大堆建构在6502处理器上的电脑,因此能设计出一颗类似的芯片即意味着对公司有很大的优势。

Acorn RISC Machine:ARM2

用在BBC Micro上的ARM1 second processor

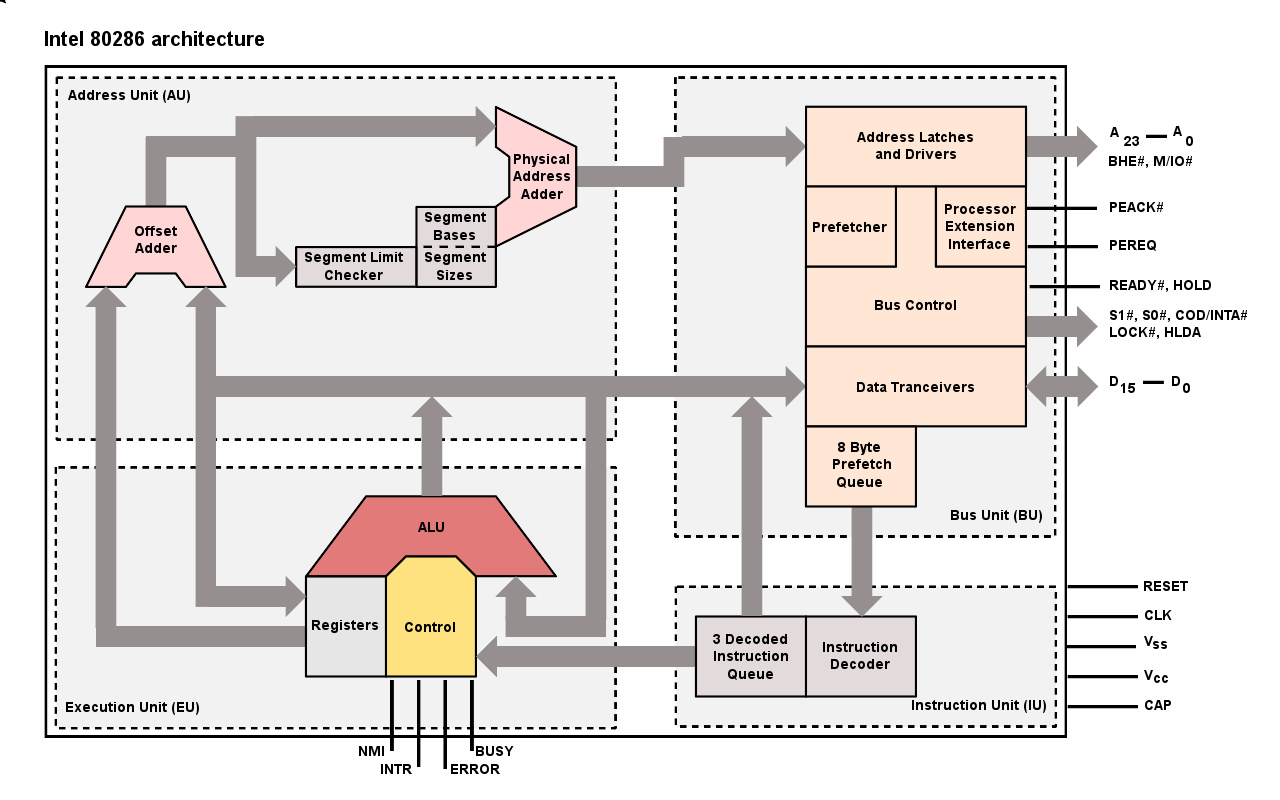

团队在1985年时开发出样本“ARM1”,而首颗真正能量产的“ARM2”于次年投产。ARM2具有32位的数据总线、26位的定址空间,并提供64 Mbyte的定址范围与16个32-bit的寄存器。寄存器中有一个作为程序计数器,其前面6位和后面2位用来保存处理器状态标记。ARM2可能是全世界最简单实用的32位微处理器,仅容纳了30,000个晶体管(六年后的摩托罗拉68000包含了70,000颗)。之所以精简的原因在于它不含微码(这大概占了68000的晶体管数约1/4至1/3);而且与当时大多数的处理器相同,它没有包含任何的高速缓存。这个精简的特色使它只需消耗很少的电能,却能发挥比Intel 80286更好的性能 。后继的处理器“ARM3”则备有4KB的高速缓存,使它能发挥更佳的性能。

Apple、DEC、Intel、Marvell:ARM6、StrongARM、XScale

在1980年代晚期,苹果电脑开始与艾康电脑合作开发新版的ARM核心。由于这项目非常重要,艾康电脑甚至于1990年将设计团队另组成一间名为安谋国际科技(Advanced RISC Machines Ltd.)的新公司。也基于这原因,使得ARM有时候反而称作Advanced RISC Machine而不是Acorn RISC Machine。由于其母公司ARM Holdings plc于1998年在伦敦证券交易所和NASDAQ挂牌上市 ,使得Advanced RISC Machines成了ARM Ltd旗下拥有的产品 。

这个项目到后来进入了“ARM6”,首版的样品在1991年发布,然后苹果电脑使用ARM6架构的ARM 610来当作他们Apple Newton产品的处理器。在1994年,艾康电脑使用ARM 610做为他们个人电脑产品的处理器。

在这些变革之后,内核部分却大多维持一样的大小——ARM2有30,000颗晶体管,但ARM6却也只增长到35,000颗。主要概念是以ODM的方式,使ARM核心能搭配一些选配的零件而制成一颗完整的CPU,而且可在现有的晶圆厂里制作并以低成本的方式达到很大的性能。

ARM的经营模式在于出售其IP核,授权厂家依照设计制作出建构于此核的微控制器和中央处理器。最成功的实现案例属ARM7TDMI,几乎卖出了数亿套内置微控制器的设备。

Digital曾购买这个架构的产权并研发出“StrongARM”。在233 MHz的频率下,这颗CPU只消耗1瓦特的电能(后来的芯片消耗得更少)。这项设计后来为了和英特尔的控诉和解而技术移转,英特尔因而利用StrongARM架构补强他们老旧的i960产品。英特尔后来开发出他们自有的高性能架构产品XScale,之后卖给了迈威尔科技。

支持智能型手机、个人数码助理和其他手持设备最常见的架构是“ARMv4”。XScale和ARM926处理器是“ARMv5TE”,而且比起建构在ARMv4的StrongARM、ARM925T和ARM7TDMI等处理器还更常见于许多高级设备上。

内核种类

由ARM提供了一个厂商汇总,是在其设计中实现ARM内核的众多厂商一个总结。

架构

从1995年开始,《ARM体系结构参考手册》是ARM文档的主要来源,提供了关于ARM处理器架构和指令集,区分接口,所有的ARM处理器的支持(如指令语义)的实现细节可能会有所不同。该体系结构随着时间的演变,并与Cortex系列的核心开始,存在三个“配置”的定义如下:

"应用"配置: Cortex-A 系列

"嵌入式"配置: Cortex-R 系列

"微处理器"配置: ARM Cortex-M 系列。

每个配置允许有其子集的架构。例如,用于ARMv6-M配置(所使用的Cortex M0 / M0+/ M1)的一个子集ARMv7-M架构(支持较少的指令)。

CPU模式

CPU ARM架构指定了以下的CPU模式。在任何时刻,CPU只可处于某一种模式,但可由于外部事件(中断)或编程方式进行模式切换。

指令集

讲求精简又快速的设计方式,整体电路化却又不采用微码,就像早期使用在艾康微电脑的8位6502处理器。

ARM架构包含了以下精简指令集处理器的特性:

读取/存储架构

不支持地址不对齐存储器访问(ARMv6内核现已支持)

大量的16 × 32-bit寄存器堆

固定的32 bits操作码(opcode)长度,降低编码数量所产生的耗费,减轻解码和流水线化的负担。

大多均为一个CPU周期运行。

为了补强这种简单的设计方式,相较于同时期的处理器如Intel 80286和Motorola 68020,还多加了一些特殊设计:

大部分指令可以条件式地运行,降低在分支时产生的负重,弥补分支预测器的不足。

算数指令只会在要求时更改条件编码

32-bit筒型位移器可用来运行大部分的算数指令和定址计算而不会损失性能

强大的索引寻址模式

支持快速叶端函数调用的链寄存器

精简但快速的双优先级中断子系统,具有可切换的寄存器组

算术指令

寄存器

寄存器 R0-R7 对于所有CPU模式都是相同的,它们不会被分块。

对于所有的特权CPU模式,除了系统CPU模式之外,R13和R14都是分块的。也就是说,每个因为一个异常(exception)而可以进入模式,有其自己的R13和R14。这些寄存器通常分别包含堆栈指针和函数调用的返回地址。

同名的名称:

R13 也被指为 SP(Stack Pointer)

R14 也被指为 LR(Link Register)

R15 也被指为 PC(Program Counter)

有条件运行

有个附加在ARM设计中好玩的东西,就是使用一个4-bit 条件编码 在每个指令前头,表示每支指令的运行是否为有条件式的

这大大的减低了在存储器访问指令时用到的编码位,换句话说,它避免在对小型叙述如 if 做分支指令。有个标准的示例引用欧几里得的最大公因数算法:

在C语言中,循环为:

intgcd(inti,intj){while(i!=j)if(i>j)i-=j;elsej-=i;returni;}

在ARM汇编语言中,循环为:

loop:CMPRi,Rj;設定條件為"NE"(不等於)if(i!=j);"GT"(大於)if(i>j),;或"LT"(小於)if(i<j)SUBGTRi,Ri,Rj;若"GT"(大於),i=i-j;SUBLTRj,Rj,Ri;若"LT"(小於),j=j-i;BNEloop;若"NE"(不等於),则继续循环

这避开了 then 和 else 子句之间的分支。

其他特色

另一项指令集的特色是,能将位移(shift)和回转(rotate)等功能并成"数据处理"型的指令(算数、逻辑、和寄存器之间的搬移),因此举例来说,一个C语言的叙述

a+=(j<<2);

在ARM之下,可简化成只需一个word和一个cycle即可完成的指令

ADDRa,Ra,Rj,LSL#2

这结果可让一般的ARM程序变得更加紧密,而不需经常使用存储器访问,流水线也可以更有效地使用。即使在ARM以一般认定为慢速的速度下运行,与更复杂的CPU设计相比它仍能运行得不错。

ARM处理器还有一些在其他RISC的架构所不常见到的特色,例如程序计数器-相对定址(的确在ARM上程序计数器为16个寄存器的其中一个)以及前递加或后递加的定址模式。

另外值得注意的是ARM处理器会随着时间不断地增加它的指令集。譬如某些早期的ARM处理器(比ARM7TDMI更早),可能并未具备指令可以读取2 Bytes的数量;因此严格来讲,对这些处理器产生代码时,就不可能处理如C语言对象中使用“volatile short”的数据类型。

流水线

ARM7和大多数较早的设计具备三阶段的流水线:提取指令、解码,并运行。较高性能的设计,如ARM9,则有更深阶段的流水线: Cortex-A8有13阶段的流水线。提高性能的额外方式,包含一颗较快的加法器,和更广的分支预测逻辑线路。例如,在ARM7DI核与ARM7DMI核之间的差异,是一种改进的乘法器(因此添加的“M”)。

辅助处理器

这个架构使用“辅助处理器”提供一种非侵入式的方法来延伸指令集,可通过软件下MCR、MRC、MRRC和MCRR等指令来对辅助处理器定址。辅助处理器空间逻辑上通常分成16个辅助处理器,编号分别从0至15;而第15号辅助处理器是保留用作某些常用的控制功能,像是使用高速缓存和记忆管理单元运算(若包含于处理器时)。

在ARM架构的机器中,周边设备连接处理器的方式,通常通过将设备的实体寄存器对应到ARM的存储器空间、辅助处理器空间,或是连接到另外依序接上处理器的设备(如总线)。辅助处理器的访问延迟较低,所以有些周边设备(例如XScale中断控制器)会设计成可通过不同方式访问(通过存储器和辅助处理器)。

调试

Thumb

较新的ARM处理器有一种16-bit指令模式,叫做Thumb,也许跟每个条件式运行指令均耗用4位的情形有关。在Thumb模式下,较小的opcode有更少的功能性。例如,只有分支可以是条件式的,且许多opcode无法访问所有CPU的寄存器。然而,较短的opcode提供整体更佳的编码密度(注:意指代码在存储器中占的空间),即使有些运算需要更多的指令。特别在存储器端口或总线宽度限制在32以下的情形时,更短的Thumb opcode能更有效地使用有限的存储器带宽,因而提供比32位代码更佳的性能。典型的嵌入式硬件仅具有较小的32-bit datapath定址范围以及其他更窄的16 bits定址(例如Game Boy Advance)。在这种情形下,通常可行的方案是编译成Thumb代码,并自行最优化一些使用(非Thumb)32位指令集的CPU相关程序区,因而能将它们置入受限的32-bit总线宽度的存储器中。

首颗具备Thumb技术的处理器是ARM7TDMI。所有ARM9和后来的家族,包括XScale,都纳入了Thumb技术。

Jazelle

ARM还开发出一项技术,Jazelle DBX(Direct Bytecode eXecution),允许它们在某些架构的硬件上加速运行Java bytecode,就如其他运行模式般,当调用一些无法支持bytecodes的特殊软件时,能提供某些bytecodes的加速运行。它能在现存的ARM与Thumb模式之间互相运行。

首颗具备Jazelle技术的处理器是“ARM7EJ-S”:Jazelle以一个英文字母"J"标示于CPU名称中。它用来让手机制造商能够加速运行Java ME的游戏和应用程序,也因此促使了这项技术不断地开发。

Thumb-2

Thumb-2技术首见于“ARM1156核心”,并于2003年发表。Thumb-2扩充了受限的16位Thumb指令集,以额外的32位指令让指令集的使用更广泛。因此Thumb-2的预期目标是要达到近乎Thumb的编码密度,但能表现出近乎ARM指令集在32位存储器下的性能。

Thumb-2至今也从ARM和Thumb指令集中衍伸出多种指令,包含位段操作、分支建表和条件运行等功能。

Thumb Execution Environment(ThumbEE)

ThumbEE,也就是所谓的Thumb-2EE,业界称为Jazelle RCT技术,于2005年发表,首见于“Cortex-A8”处理器。ThumbEE提供从Thumb-2而来的一些扩充性,在所处的运行环境下,使得指令集能特别适用于运行阶段的编码产生(例如即时编译)。Thumb-2EE是专为一些语言如Limbo、Java、C#、Perl和Python,并能让即时编译器能够输出更小的编译码却不会影响到性能。

ThumbEE所提供的新功能,包括在每次访问指令时自动检查是否有无效指针,以及一种可以运行数组范围检查的指令,并能够分支到分类器,其包含一小部分经常调用的编码,通常用于高级语言功能的实现,例如对一个新对象做存储器配置。

高级SIMD(NEON)

高级SIMD延伸集,业界称为“NEON”技术,它是一个结合64位和128位的单指令多重数指令集(SIMD),其针对多媒体和信号处理程序具备标准化加速的能力。NEON可以在10 MHz的处理器上运行MP3音效解码,且可以运行13 MHz以下的自适应多速率音频压缩编码。NEON具有一组广泛的指令集、各自的寄存器阵列,以及独立运行的硬件。NEON支持8、16、32和64位的整数及单精度浮点数据,并以单指令多重数的方式运算,运行图形和游戏处理中关于语音及视频的部分。单指令多重指令集在向量超级处理机中是个决定性的要素,它具备同时多项处理功能。在NEON技术中,SIMD最高可同时做16个运算。

VFP

VFP(向量浮点)是在协同处理器针对ARM架构的派生技术。它提供低成本的单精度和倍精度浮点运算能力,并完全兼容于ANSI/IEEE Std 754-1985二进制浮点算数标准。VFP提供大多数适用于浮点运算的应用,例如PDA、智能手机、语音压缩与解压、3D图像以及数字音效、打印机、机顶盒,和汽车应用等。VFP架构也支持SIMD平行化的短向量指令运行。这在图像和信号处理等应用上,非常有助于降低编码大小并增加输出效率。

在ARM为基础的处理器中,其他可见的浮点、或SIMD的协同处理器还包括了FPA、FPE、iwMMXt。他们提供类似VFP的功能,但在opcode层面上来说并不具有兼容性。

安全性扩充(TrustZone)

TrustZone技术出现在ARMv6KZ以及较晚期的应用核心架构中。它提供了一种低成本的方案,针对系统单片机内加入专属的安全核心,由硬件建构的访问控制方式支持两颗虚拟的处理器。这个方式可使得应用程序核心能够在两个状态(领域)之间切换,在此架构下可以避免信息从较可信的核心领域泄漏至较不安全的领域。这种内核领域之间的切换通常是与处理器其他功能完全无关系性,因此各个领域可以各自独立运作但却仍能使用同一颗内核。存储器和周边设备也可因此得知目前内核运作的领域为何,并能针对这个方式来提供对设备的机密和编码进行访问控制。典型的TrustZone技术应用是要能在一个缺乏安全性的环境下完整地运行操作系统,并在可信的环境下能有更少的安全性的编码。T6 是中国第一个开源的TrustZone安全内核。

ARM授权方式

ARM公司本身并不靠自有的设计来制造或出售CPU,而是将处理器架构授权给有兴趣的厂家。ARM提供了多样的授权条款,包括售价与散播性等项目。对于授权方来说,ARM提供了ARM内核的集成硬件叙述,包含完整的软件开发工具(编译器、debugger、SDK),以及针对内含ARM CPU硅芯片的销售权。对于无晶圆厂的授权方来说,其希望能将ARM内核集成到他们自行研发的芯片设计中,通常就仅针对获取一份生产就绪的智财核心技术(IP Core)认证。对这些客户来说,ARM会发布所选的ARM核心的闸极电路图,连同抽象模拟模型和测试程序,以协助设计集成和验证。需求更多的客户,包括集成组件制造商(IDM)和晶圆厂家,就选择可合成的RTL(寄存器传输级,如Verilog)形式来获取处理器的知识产权(IP)。借着可集成的RTL,客户就有能力能进行架构上的最优化与加强。这个方式能让设计者完成额外的设计目标(如高震荡频率、低能量耗损、指令集延伸等)而不会受限于无法更动的电路图。虽然ARM并不授予授权方再次出售ARM架构本身,但授权方可以任意地出售制品(如芯片组件、评估板、完整系统等)。商用晶圆厂是特殊例子,因为他们不仅授予能出售包含ARM内核的硅晶成品,对其它客户来讲,他们通常也保留重制ARM内核的权利。

就像大多数IP出售方,ARM依照使用价值来决定IP的售价。在架构上而言,更低性能的ARM内核比更高性能的内核拥有较低的授权费。以硅芯片实现而言,一颗可集成的内核要比一颗硬件宏(黑箱)内核要来得贵。更复杂的价位问题来讲,持有ARM授权的商用晶圆厂(例如韩国三星和日本富士通)可以提供更低的授权价格给他们的晶圆厂客户。通过晶圆厂自有的设计技术,客户可以更低或是免费的ARM预付授权费来获取ARM内核。相较于不具备自有设计技术的专门半导体晶圆厂(如台积电和联电),富士通/三星对每片晶圆多收取了两至三倍的费用。对中少量的应用而言,具备设计部门的晶圆厂提供较低的整体价格(通过授权费用的补助)。对于量产而言,由于长期的成本缩减可借由更低的晶圆价格,减少ARM的NRE成本,使得专门的晶圆厂也成了一个更好的选择。

许多半导体公司持有ARM授权:Atmel、Broadcom、Cirrus Logic、Freescale(于2004从摩托罗拉公司独立出来)、富士通、英特尔(借由和Digital的控诉调停)、IBM、NVIDIA、台湾新唐科技(Nuvoton Technology)、英飞凌、任天堂、恩智浦半导体(于2006年从飞利浦独立出来)、OKI电气工业、三星电子、Sharp、STMicroelectronics、德州仪器和VLSI等许多这些公司均拥有各个不同形式的ARM授权。虽然ARM的授权项目由保密合约所涵盖,在知识产权工业,ARM是广为人知最昂贵的CPU内核之一。单一的客户产品包含一个基本的ARM内核可能就需索取一次高达美金20万的授权费用。而若是牵涉到大量架构上修改,则费用就可能超过千万美元。

ARM内核的授权与应用

延伸阅读

新唐(Nuvoton)ARM® Cortex™-M0微控制器ICNuMicro™ Family- High Density with more functionality

Inferno

DirectBand

AMULET - 异步ARM家族

Philips LPC2000 ARM7TDMI-S Microcontrollers

Texas Instruments OMAP - 一颗加上DSP的ARM核心以及应用软件加速内核

免责声明:以上内容版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。感谢每一位辛勤著写的作者,感谢每一位的分享。

相关资料

- 有价值

- 一般般

- 没价值

推荐阅读

关于我们

APP下载