静态随机存取儲存器

设计

包含6个晶体管的CMOSSRAM基本单元

SRAM由存储矩阵、地址译码器和读/写控制电路组成,容量的扩展有两个方面:位数的扩展用芯片的并联,字数的扩展可用外加译码器控制芯片的片选输入端。SRAM中的每一bit储存在由4个场效应管(M1, M2, M3, M4)构成两个交叉耦合的反相器中。另外两个场效应管(M5, M6)是储存基本单元到用于读写的位线(Bit Line)的控制开关。

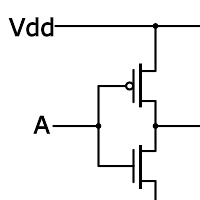

CMOS静态反相器

反相器是一种电路器件,其输出是输入的逻辑非。如图所示的CMOS静态反相器,由两个互补的金属氧化物半导体场效应管(MOSFET)组成,源极连接在高电平的是P沟道场效应管,源极连接在低电平的是N沟道场效应管。输入电路接在两个场效应管的栅极上,输出电路从两个场效应管的连接处接出。当输入低电平,则P沟道场效应管开通,N沟道场效应管关闭,输出高电平。当输入高电平,则N沟道场效应管开通,P沟道场效应管关闭,输出低电平。这就实现了“反相”输出。

一个SRAM基本单元有0 and 1两个电平稳定状态。SRAM基本单元由两个CMOS反相器组成。两个反相器的输入、输出交叉连接,即第一个反相器的输出连接第二个反相器的输入,第二个反相器的输出连接第一个反相器的输入。这就能实现两个反相器的输出状态的锁定、保存,即储存了1个位元的状态。

除了6管的SRAM,其他SRAM还有8管、10管甚至每个位元使用更多的晶体管的实现。这可用于实现多端口(port)的读写访问,如显存或者寄存器堆的多口SRAM电路的实现。

一般说来,每个基本单元用的晶体管数量越少,其占用面积就越小。由于硅芯片(silicon wafer)的生产成本是相对固定的,因此SRAM基本单元的面积越小,在硅芯片上就可以制造更多的位元存储,每位元存储的成本就越低。

内存基本单元使用少于6个晶体管是可能的—如3管甚至单管,但单管储存单元是DRAM,不是SRAM。

访问SRAM时,字线(Word Line)加高电平,使得每个基本单元的两个控制开关用的晶体管M5与M6开通,把基本单元与位线(Bit Line)连通。位线用于读取或写入基本单元的保存的状态。虽然不是必须两条取反的位线,但是这种取反的位线有助于改善噪声容限.

与动态存储器(DRAM)相比,SRAM的带宽有很大改进—由于两条位线是反相,这种差分信号使得SRAM的抗噪声干扰能力很强。而DRAM的位线连接到存储电容,受困于电荷共享(charge sharing)使得其位线信号上下波动。另一项差别使得SRAM更快是其地址线各位元是同时工作选择出目标存储单元的字线,而DRAM往往为了降低成本,是先送出低半段的地址线的各比特,然后再送出高半段的地址线的各bit,这降低了DRAM封装的地址引脚的数量。

有m条地址线与n条数据线的SRAM,其存储容量是2个字(word),2×nbit.每个字的长度至少是64bit。

SRAM操作

SRAM的基本单元有3种状态:standby (电路处于空闲), reading(读取)与writing(写入). SRAM的读取或写入模式必须分别具有"readability"(可读)与"write stability"(写入稳定)。

Standby

如果字线没有被选为高电平,那么作为控制用的M5与M6两个晶体管处于断路,把基本单元与位线隔离。由M1 – M4组成的两个反相器继续保持其状态,只要保持与高、低电平的连接。

Reading

假定储存的内容为1,即在Q处的电平为高。读取周期开始时,两条位线预充值为逻辑1,随后字线WL充高电平,使得两个访问控制晶体管M5与M6通路。第二步是保存在Q的值与位线BL的预充值相同,所以BL保持逻辑1,而Q与BL的预充值不同,使得BL经由M1与M5放电而变成逻辑0(即Q的高电平使得晶体管M1通路)。在位线BL一侧,晶体管M4与M6通路,把位线连接到VDD所代表的逻辑1(M4作为P沟道场效应管,由于栅极加了Q的低电平而M4通路)。如果储存的内容为0,相反的电路状态将会使BL为1而BL为0.只需要BL与BL有一个很小的电位差,读取的放大电路将会辨识出哪条位线是1哪条是0.敏感度越高,读取速度越快。

Writing

写入周期开始时,把要写入的状态加载到位线。如果要写入0,则设置BL为1且BL为0。随后字线WL加载为高电平,位线的状态被载入SRAM的基本单元。这是通过位线输入驱动能力设计的比基本单元相对较弱的晶体管更为强壮,使得位线状态可以覆盖基本单元交叉耦合的反相器的以前的状态。

总线行为

访问时间为70ns的RAM在位址设定完成且有效之后,会在70ns之内将资料输出。数据将继续保持有效约5-10 ns。起、落时间将影响有效时间槽(timeslot)约5 ns.如果先读入低半段地址,将会多耗费30 ns。

应用与使用

特性

SRAM是比DRAM更为昂贵,但更为快速、非常低功耗(特别是在空闲状态)。因此SRAM首选用于带宽要求高,或者功耗要求低,或者二者兼而有之。SRAM比起DRAM更为容易控制,也更是随机访问。由于复杂的内部结构,SRAM比DRAM的占用面积更大,因而不适合用于更高储存密度低成本的应用,如PC内存。

时钟频率与功耗

SRAM功耗取决于它的访问频率。如果用高频率访问SRAM,其功耗比得上DRAM。有的SRAM在全带宽时功耗达到几个瓦特量级。另一方面,SRAM如果用于温和的时钟频率的微处理器,其功耗将非常小,在空闲状态时功耗可以忽略不计—几个微瓦特级别。

SRAM用于:

通用的产品

集成于芯片内

嵌入式应用

工业与科学用的很多子系统,汽车电子等等都用到了SRAM。现代设备中很多都嵌入了几千字节的SRAM。实际上几乎所有实现了电子用户界面的现代设备都可能用上了SRAM,如玩具。数码相机、手机、音响合成器等往往用了几兆字节的SRAM。 实时信号处理电路往往使用双口(dual-ported)的SRAM。

用于计算机

SRAM用于PC、工作站、路由器以及外设:内部的CPU高速缓存,外部的突发模式使用的SRAM缓存,硬盘缓冲区,路由器缓冲区,等等。LCD显示器或者打印机也通常用SRAM来缓存数据。SRAM做的小型缓冲区也常见于CDROM与CDRW的驱动器中,通常为256 KiB或者更多,用来缓冲音轨数据。线缆调制解调器及类似的连接于计算机的设备也使用了SRAM。

爱好者

搭建自己的处理器的业余爱好者更愿意选用SRAM,这是由于其易用性的工作界面。没有DRAM所需的刷新周期;地址总线与数据总线直接访问而不是像DRAM那样多工分别访问。SRAM通常只需3个控制信号:Chip Enable (CE), Write Enable (WE)与Output Enable(OE)。对于同步SRAM,还需要时钟信号(Clock,CLK)。

SRAM的类型

非挥发性SRAM

非挥发性SRAM(Non-volatile SRAM,nvSRAM)具有SRAM的标准功能,但在失去电源供电时可以保住其数据。非挥发性SRAM用于网络、航天、医疗等需要关键场合—保住数据是关键的而且不可能用上电池。

异步SRAM

异步SRAM(Asynchronous SRAM)的容量从4 Kb到64 Mb。SRAM的快速访问使得异步SRAM适用于小型的cache很小的嵌入式处理器的主内存,这种处理器广泛用于工业电子设备、测量设备、硬盘、网络设备等等。

根据晶体管类型分类

双极性结型晶体管(用于TTL与ECL)—非常快速但是功耗巨大

MOSFET(用于CMOS)—本文详细介绍的类型,低功耗,现在应用广泛。

根据功能分类

异步—独立的时钟频率,读写受控于地址线与控制使能信号。

同步—所有工作是时钟脉冲边沿开始,地址线、数据线、控制线均与时钟脉冲配合。

根据特性分类

零总线翻转(Zero bus turnaround,ZBT)—SRAM总线从写到读以及从读到写所需要的时钟周期是0

同步突发SRAM(synchronous-burst SRAM,syncBurst SRAM)—

DDR SRAM—同步、单口读/写,双数据率I/O

QDR SRAM(Quad Data Rate (QDR) SRAM)—同步,分开的读/写口,同时读写4个字(word)。

根据触发类型

二进制SRAM

三进制计算机SRAM

参见

DRAM,包括PSRAM (pseudo-static RAM)

闪存

晶体管

免责声明:以上内容版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。感谢每一位辛勤著写的作者,感谢每一位的分享。

- 有价值

- 一般般

- 没价值

24小时热门

推荐阅读

关于我们

APP下载