移位寄存器

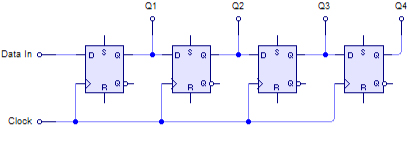

串入串出

破坏性读出

这是最简单的移位寄存器类型。出现在“数据输入”的数据串每次“数据移位”都会向右移动升高一级。每次移位过程中,最左边的一位(即“数据输入”)移入第一个触发器的输出中。最右边的一位(即“数据输出”)会移出并丢失。

数据存储在每个触发器后的“Q”输出中,所以在这种排列下有四个可以使用的“储存槽”,因此为4位寄存器。要对移位模式有所了解,可以想象寄存器内数据为 0000(则所有储存槽都为空)。随着“数据输入”出现 1,0,1,1,0,0,0,0,对于寄存器(按照这个顺序,每次“数据移位”都有一个脉冲,称作选通),这就是结果。左边的列对应于最左边的触发器的输出引脚,后面同理。

所以整个寄存器的串行输出为 10110000。可以看出如果数据输入是连续的,就会得到完整的输入,只是偏移了四个“数据移位”周期。这种排列是队列的硬件等价形式。同时,在任何时候,整个寄存器可以通过复位引脚设置为高电平来置零(R)。

这种排列展现出“破坏性读出”——所有数据在被移位到最右面的位之后就会丢失。

串入并出

4位的串入并出移位寄存器

串入并出形式的移位寄存器接法,可以将输入的串行数据以并行格式输出。串行通信要求的几位数据完成输入之后,就可以在输出端的各位同时读出并行数据。

在这种设置中,每个触发器都是边沿触发的。第一个触发器工作在给定的时钟频率下。其余后级触发器将前级的频率折半,也就是占空比变为二倍。因此,它需要两倍长的上升/下降沿来触发后续的每一个触发器;这就错开了时域中的串行输入,从而导致并行输出。

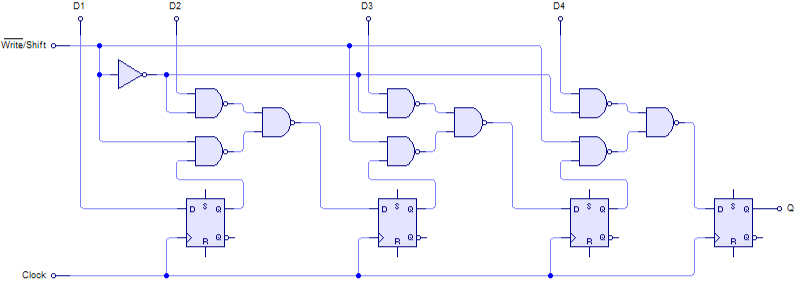

并入串出

并入串出形式的移位寄存器接法,通过下图所示D1-D4并行输入段接收4位外部并行数据,而Q为串行输出的引脚。为了将数据写入到寄存器中,写/移位控制线必须保持低电平。写入完成,需要移位时,写/移位控制线则必须处于高电平,而且必须给予时间脉冲,每提供一个时间脉冲,向左(或向右)移动一位。

4位的并入串出移位寄存器

下图展示了写/移位序列的变化情况,并显示了移位寄存器内部的情况。

下边的红字表示输入数据,右上角的数字表示以串行方式依次输出的数据

应用

移位寄存器一个最普遍的应用,是数据传输过程中,串行接口和并行接口的转换。这在许多并行传输一组比特数据的电路中很有用,因为它们常常也使用了在结构上更为简单的串行接口。移位寄存器可以被用作一个简单的延迟电路。许多双向移位寄存器可以在并行传输中作为堆栈的硬件实现方式。

串入并出形式的移位寄存器经常与微处理器连接,这样做的原因主要是需要的引脚数多于微处理器能够提供的数量。通过使用移位寄存器,可以只依靠两三个引脚,而设备的控制位分别连接在移位寄存器的并行输出端。由此,微处理器可以以串行的方式一次写入这些设备的各个控制位。类似的,并入串出接法的移位寄存器在多个外部设备向微处理器传输数据时较为常用,外部设备以并行的方式将数据输入到移位寄存器里,然后移位寄存器以串行的方式将数据一位一位地输出给微处理器,这样,外部设备的大量信息可以通过少数几条线到达微处理器。

在早期的计算机中,移位寄存器被用来进行数据处理:两个相加的数被存储在两个移位寄存器里,然后它们按照时间脉冲被输出到算术逻辑单元,结果中多出的一位以反馈的形式重新被输入到其中一个移位寄存器(累加器)。注意两个一位二进制数相加的结果只可能是一位(如0+0=0,0+1=1)或者两位(1+1=10)。

一些计算机语言内置了移位指令,这类指令可以让二进制数据在寄存器中进行左移或右移操作。左移或右移一位,相当于乘以2或除以2。

一些1970年代早期的设备曾以类似延迟线存储器的方式用过非常大规模的串入串出移位寄存器,其规模达到上千位。这类存储器有时被称为循环存储器(circulating memory)。例如,DataPoint 3300将其25列、72行的字符显示数据存储在54个200位的移位寄存器里,以6个堆栈、每个堆栈9个包的形式排列,提供了1800个6位字符的存储能力。

相关条目

线性反馈移位寄存器(LFSR)

环形计数器(英语:Ring counter)

免责声明:以上内容版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。感谢每一位辛勤著写的作者,感谢每一位的分享。

- 有价值

- 一般般

- 没价值

关于我们

APP下载