Sandy Bridge微架构

技术特点

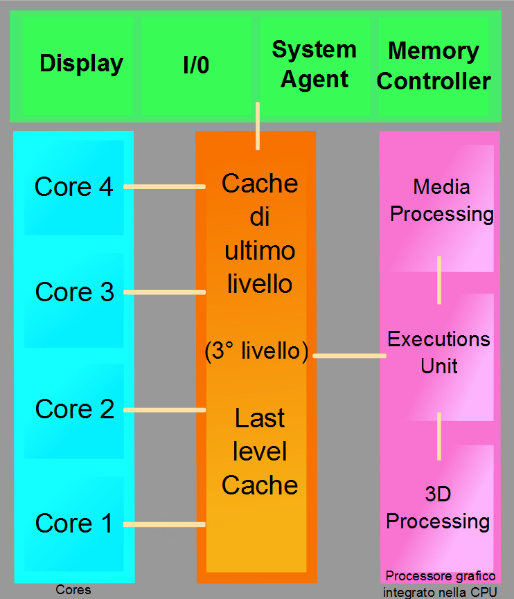

Sandy Bridge四核心微架构图解

Intel Sandy Bridge微架构的研发主要由Intel的以色列分公司的研发中心负责,原先Sandy Bridge代号为‘Gesher’(希伯来语中意为‘桥梁’)。后来为避免让人联想到以色列已解散政党‘Gesher political party’,遂改为现在的代号名称。 研发计划组由Intel副总裁罗恩·弗里德曼领导并管理。 2009年9月在Intel开发者论坛上,Intel展示了使用Sandy Bridge微架构的工程样品处理器,展示的工程样品处理器为A1步进,并运作于2.0GHz的时钟频率上。

缓存

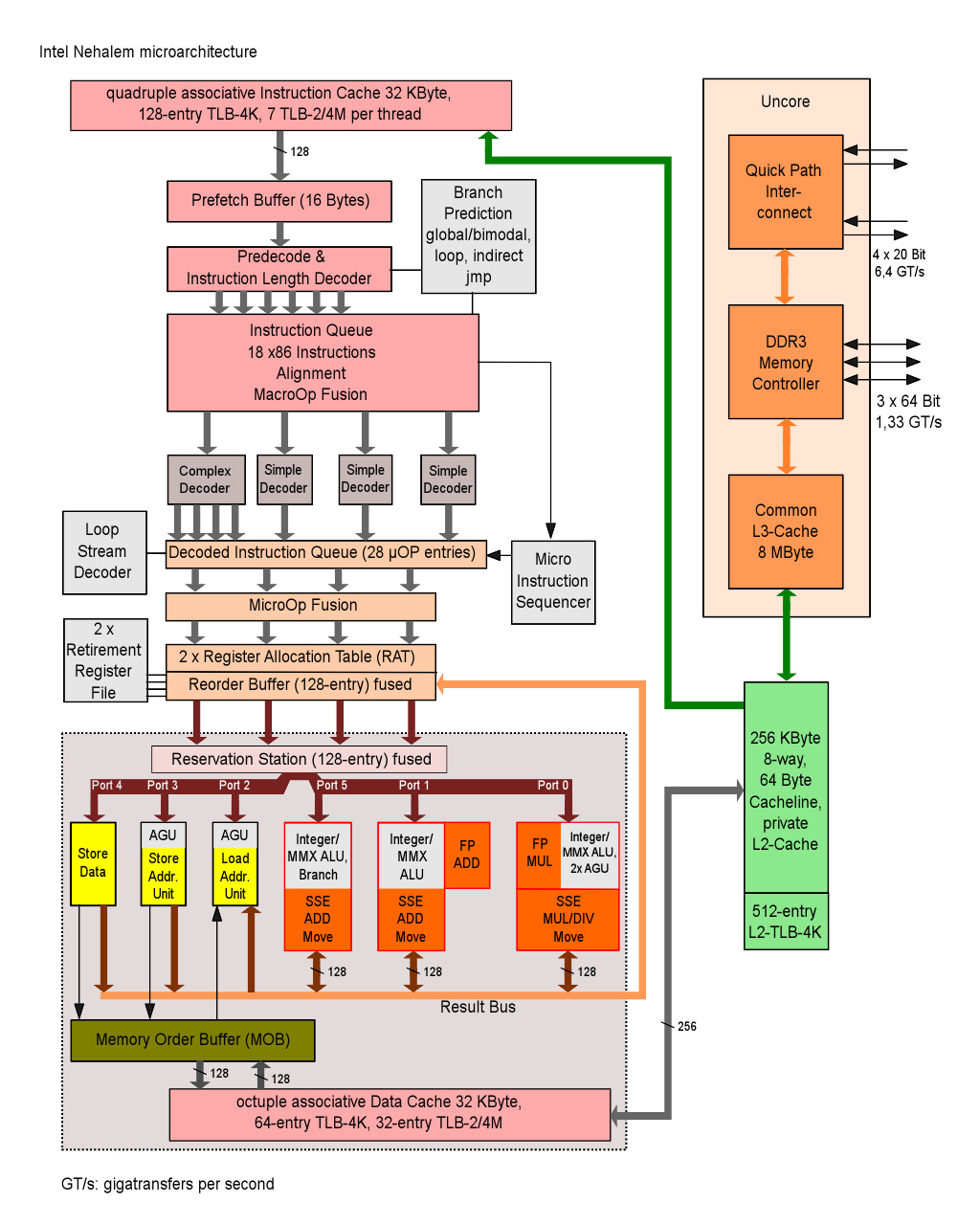

与Intel Nehalem微架构的相近,L1缓存仍为每核心64KB(32KB数据缓存+32KB指令缓存),L2缓存每核心独占256KB,内置共用式L3缓存,最高可达20MB。

多线程/超线程

部分型号的处理器(如Core i3、Core i7等)会继续沿袭超线程技术,最高可达8核心,16线程。

融合显示核心

在Intel Nehalem的制程改进版Intel Westmere上分立的显示芯片和CPU芯片的设计,在Intel Sandy Bridge上以GPU和CPU完整融合进一块芯片上的设计所替换,而且在Intel Sandy Bridge上显示核心将与CPU共用L3缓存,显示核心官方品牌名称为‘核芯显卡’。移动平台的处理器均采用这种设计,而这种设计在桌面平台仅见于LGA1155平台。

硬件视频加速

Intel在Sandy Bridge上新增了Intel Quick Sync Video(快速视频同步)技术,支持硬件加速视频编码/解码。

北桥

延续Intel Nehalem的设计,存储器控制器和PCI Express控制器集成于CPU核心中,而且在Sandy Bridge上,存储器控制器的性能进一步提升,每个存储器通道每时钟周期支持两次访问操作。最高可支持四通道DDR3-2133。PCI-E 3.0 Lanes有40根,暂时较16根的ivy bridge(x8+x8/x8+x4+x4)高。

总线

仍然使用QPI/DMI总线,但处理器内部则改为环形总线(Ring Bus)的形式,单向传输位宽为256比特。处理器上各核心、GPU、缓存、存储器控制器、PCI Express控制器以及各种在处理器上的输出输入控制器等均以环形总线连接。

核心

对分支预测器的设计进一步优化,扩大微码解码器缓存。电源和性能管理方面Turbo Boost(涡轮加速/睿频)则升级为2.0版本。

指令集

提升处理器运算超越函数的性能,优化AES加密性能(AES指令集)和SHA-1切细性能;新增256比特指令集AVX指令集,增强矢量运算能力和浮点运算能力。

芯片组、处理器插座

Sandy Bridge微架构的i7-2600K,采用LGA 1155

Intel为Sandy Bridge微架构的处理器推出了6系列消费级芯片组和C200系列企业级芯片组。处理器插座也顺势更变:桌面型平台、服务器平台、工作站平台的为LGA1155、LGA2011、LGA1356(仅服务器、工作站平台);移动平台的为BGA 1023/Socket G2、BGA 1224以及rPGA988B。

CPUID和步进

几乎所有的Sandy Bridge微架构的单核、双核甚至是四核的处理器都使用了同样为 0206A7h 的CPUID 。这些信息使得不能由CPUID直接识别处理器型号,但仍可以通过PCI配置空间来识别。后来极致性能/服务器平台的Sandy Bridge-E,最高可达八核心十六线程,无集成显示核心的处理器则使用 0206D6h 和 0206D7h 的CPUID。 详细的信息如列表所示:

性能

平均性能表现继续提升,根据IXBT Labs和Semi Accurate等众多媒体的基准测试,每时钟周期的性能比上代的Nehalem微架构高出平均11.3%,包括Nehalem微架构家族之中代号的Bloomfield、Clarkdale和Lynnfield等一众处理器。 但相比Intel Nehalem与Intel Core巨大的性能落差,Intel Sandy Bridge与Intel Nehalem的性能落差相对小得多。由于AMD的Bulldozer微架构迟迟未能推出,加之原来的K10.5架构日渐老旧以及Bulldozer微架构推出后其性能表现不佳,使Intel Sandy Bridge的高级型号的处理器在x86处理器领域几近毫无对手(但是相对于整个处理器领域,目前仍落后于不少大型精简指令集体系的处理器,如IBM POWER 7)。

集成的显示核心升格为Intel HD Graphics 2000/3000,运行单元为6个和12个,但其性能表现相比Intel Westmere的Intel HD Graphics 1000相比几近翻倍,但仍不及AMD Fusion集成的Radeon HD 6550D/6530D等集成显示核心。

处理器列表

芯片组缺陷

2011年1月31日,Intel突然发布关于6系列芯片组的召回通知,原因是PCH芯片组上SATA控制器的瑕疵。

这个SATA控制器的问题,在于其SATA 3Gbps连接端口会随时发生故障而使主板失去与硬盘驱动器等设备的连接,尽管不会造成数据丢失等严重后果,而且SATA 6Gbps连接端口并没有这个问题。 Intel认为这个瑕疵仅会使5%的用户在使用3年后才会出现问题,但尽管如此,重度输出输入负载会使这个问题更早暴露出来。

出现该问题的6系列芯片组批量属于正式发售的B2步进版本,原来的工程样品并没有发现该问题的存在。Intel事后也迅速停止了B2步进版本的6系列芯片组的生产,改为生产经过电路修正后的B3步进的6系列芯片组。对主板厂商和OEM主机厂商,对于已出货的B2步进批量,Intel给予采购厂商有偿退换B3步进批量的产品,召回和退换行动由2011年2月14日开始,截止至2011年4月,在Intel确认已回收完所有B2步进批量的6系列芯片组以后。 在销售终端方面,主板厂商(例如华硕、技嘉等厂商)以及OEM品牌主机厂商(如DELL、HP等)则停止销售并回收在架的产品,由于Intel的召回行动并没有针对消费者,所以这些厂商有的自身出资为用户更换问题主板,有的则对问题主板用户提供技术支持(但可以选择自行与厂商联系更换)等。

由于芯片组的瑕疵,使得日后Sandy Bridge微架构处理器的销售受到了一定影响,毕竟要使用Sandy Bridge微架构处理器必须使用6系列/7系列(2011年第四季度推出)的芯片组,对于Nehalem微架构的5系列芯片组Intel则不予支持。尽管如此,新架构处理器的发布照常进行,并没有受到影响。 问题被公布以后的两个星期,一些问题芯片组仍有少量出货,但主板厂商却要接受Intel的一系列条款,保证没有用户遇到芯片组出现问题的情况出现。

限制

超频

Intel从Sandy Bridge微架构开始,处理器与PCH芯片组、芯片组与各系统总线之间统一使用DMI总线连接,而且还把系统总线(包括USB、SATA、PCI、PCI-E、CPU核心外频、存储器控制器等)的时钟频率统一由PCH芯片组内置的时钟频率发生器(DMICLK)产生,基准为100MHz,不再外加时钟频率发生器CK505 External。 在处理器的倍频被锁定的情况下,提升时钟频率只能通过提升基准时钟频率,在Sandy Bridge微架构上,由于一改变基准时钟频率(DMI总线时钟频率)就会连带改变所有系统总线的时钟频率,而部分系统总线(如SATA、PCI-E)并不能承受更高的时钟频率,致使基准时钟频率的提升空间被大大限制(仅能提升5%至7%),尽管DDR3系统存储器的时钟频率倍率没有限制。为照顾超频用户,Intel也顺势推出了不锁倍频的K/X系列处理器,允许用户可以调整出超过涡轮加速最大倍频的倍频值,但最高倍频仍限制在57x。 而在Sandy Bridge-E平台,限制相对放宽,Intel在BIOS/EFI中提供了几个基准频率的值以供用户选择。

在2010年的IDF上,Intel曾展示了一块未知型号的基于Sandy Bridge微架构的处理器,在风冷情况下稳定运作在4.9GHz上。

芯片组

在6系列芯片组中,全线均采用LGA1155之处理器插座。H6X系列型号的H61芯片组不支持RAID,H67和H61既不支持超频(即使是不锁倍频的K系列处理器),也不支持涡轮加速技术(即使处理器支持),但支持核芯显卡显示输出;而P6X系列则支持H6X所不支持的功能,但不支持核芯显卡的显示输出;而Z6X系列则支持P6X和H6X的所有功能。

2012年中期推出的7系列全系列芯片组,除了供Intel Ivy Bridge使用以外,还可与Intel Sandy Bridge兼容,其中的H7X、Z7X型号的芯片组全面支持显示信号输出,以及Turbo Boost(除H7X型号之芯片组以外)。而2011年后期发布的供Sandy Bridge-E处理器使用的X79芯片组,采用LGA2011插座,无显示输出支持,除了支持K/X系列不锁倍频的处理器,还支持多个基准时钟频率默认值的调整,这些值由Intel官方默认。

此外,P6X、Z6X系列芯片组还可以支持非K系列处理器的倍频调整,但最多只能到达涡轮加速的倍频上限。7系列芯片组类似。

Intel Insider和远程控制

Intel在Sandy Bridge微架构中还集成了一个名为Intel Insider的DRM服务,公司宣称这是“一层额外的内容保护层”。

Intel Sandy Bridge微架构处理器均带有vPro功能,出于安全目的,该功能可以从远程停止PC的使用或者是从磁盘驱动器上擦除数据,这个功能在PC丢失或被盗窃的情况下不失为一个实用的功能,处理器可以通过接受3G信号、以太网或者是互联网连接接收这些命令;此外新增的AES指令集可以在此时“大展拳脚”,充分展示处理器进行AES硬件加速加密/解密的能力,这对于企业内部的电视会议、VoIP应用等方面非常实用。

继任微架构

Intel依照Tick-Tock策略,于2012年发布Sandy Bridge微架构的制程改进版Ivy Bridge;而2013年Intel将会发布全新的Haswell微架构,替换现行的Sandy Bridge以及Ivy Bridge。

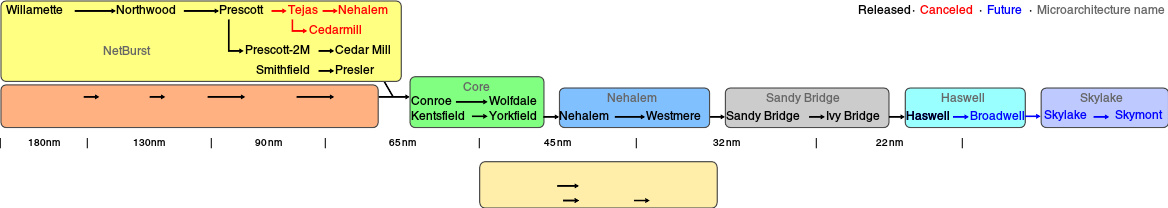

Intel的微处理器架构路线图,从 NetBurst 以及 P6 至 Skylake

免责声明:以上内容版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。感谢每一位辛勤著写的作者,感谢每一位的分享。

- 有价值

- 一般般

- 没价值

推荐阅读

关于我们

APP下载